The Ultimate 8-Layer PCB Stackup Guide for High-Speed Design

Introduction

An 8-layer PCB stackup is essential for controlling impedance, reducing EMI, and improving signal integrity. This is why it is the top choice for complex, high-speed electronic systems.

In this guide, we will show you how to optimize your 8-layer stackup. Learn how to build more stable and reliable multi-layer PCB solutions for your next project.

Why Stackup Design is Critical for High-Speed Circuits

When signal frequency reaches hundreds of MHz or even GHz, PCB stackup design is no longer just stacking copper layers together. It becomes the process of building a controlled electromagnetic environment.

High-speed signals like PCIe, USB 3.0, and DDR memory require precise impedance—usually 50Ω single-ended or 100Ω differential.To keep impedance consistent across the board, you must choose the right thickness and dielectric constant for every layer (Core and Prepreg). If the impedance does not match, the signal will reflect. This leads to poor signal integrity and high error rates.

From an electromagnetic point of view, high-speed current always returns through the path with the lowest impedance. For high-speed signals, the return current usually flows on the reference plane (GND or power plane) directly under the signal trace. A good stackup keeps the signal layer tightly coupled to its reference plane. The closer the distance, the stronger the coupling and the more stable the return path. If the stackup is not designed properly, the return current may be forced to detour. This creates larger loop inductance, which can cause serious EMI and signal distortion.

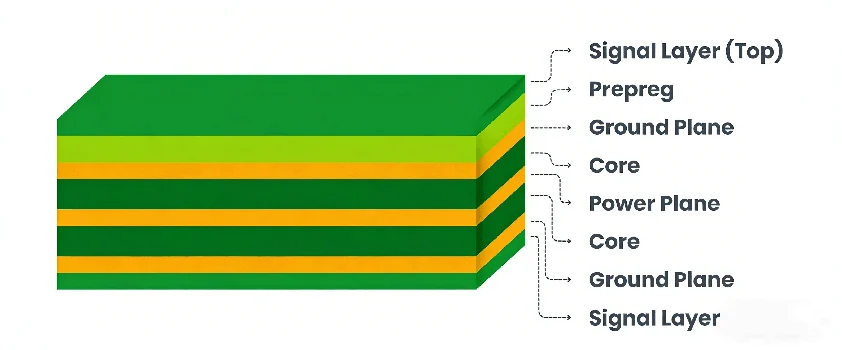

Typical 8-Layer PCB Stackup Configuration

Choosing the right PCB stackup is the foundation of a successful 8-layer PCB design. A well-planned stackup helps control impedance, reduce EMI, and ensure reliable high-speed signal transmission.To help you balance performance, cost, and manufacturability, we summarize several proven structures used in the industry. Below are three recommended 8-layer PCB stackup configurations for different application needs.

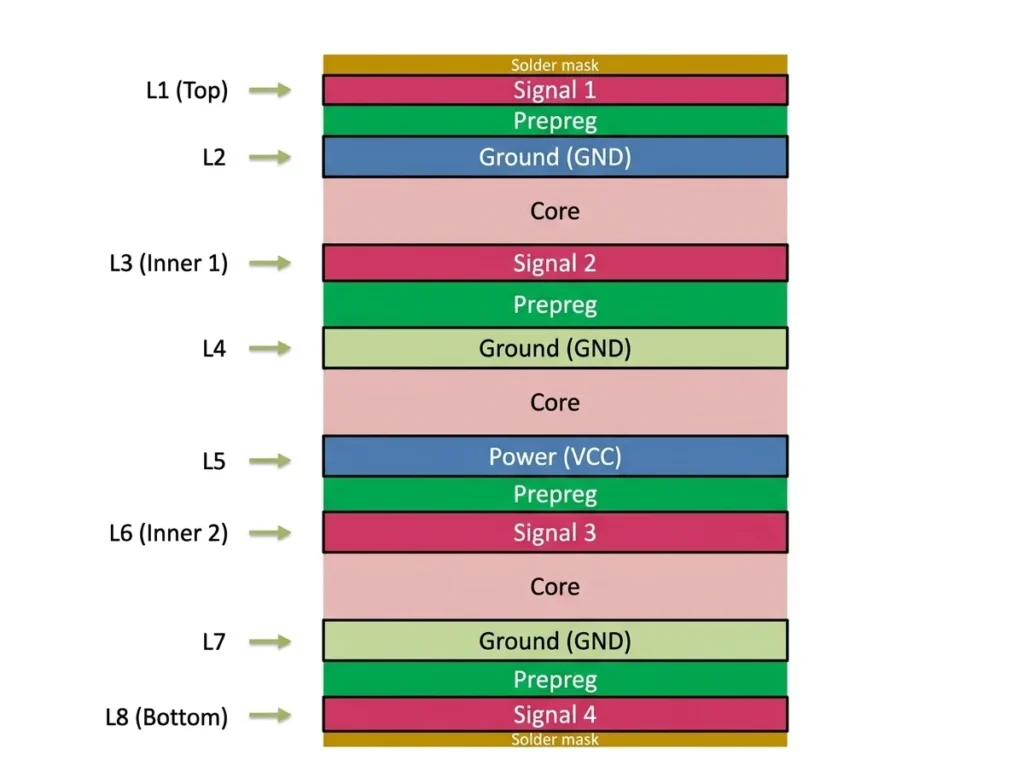

Example1: Standard High-Performance Stackup

This is the most commonly used configuration in the industry. Its main advantage is excellent EMI shielding. All inner signals (Signal 2 & 3) are sandwiched between two ground planes (Stripline structure), providing the shortest return path. It is ideal for high-density, high-speed PCB designs.

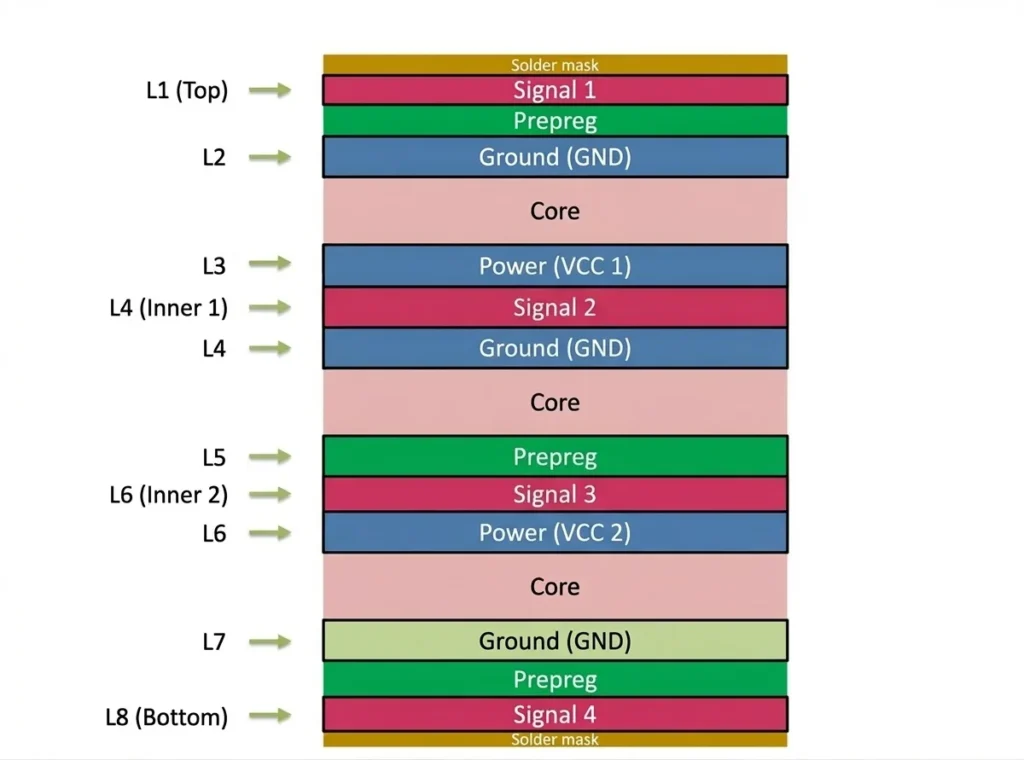

Example2: Power-Enhanced Type

If your design includes high power output, such as high-performance FPGA boards or server motherboards, this stackup can provide more stable power performance.The power and ground planes appear in pairs (Layer 2/3 and Layer 7/8), which increases interlayer capacitance and helps reduce power noise.However, the two inner signal layers (Signal 2 & 3) may have a risk of crosstalk. It is recommended to route these layers in perpendicular directions (X-Y routing).

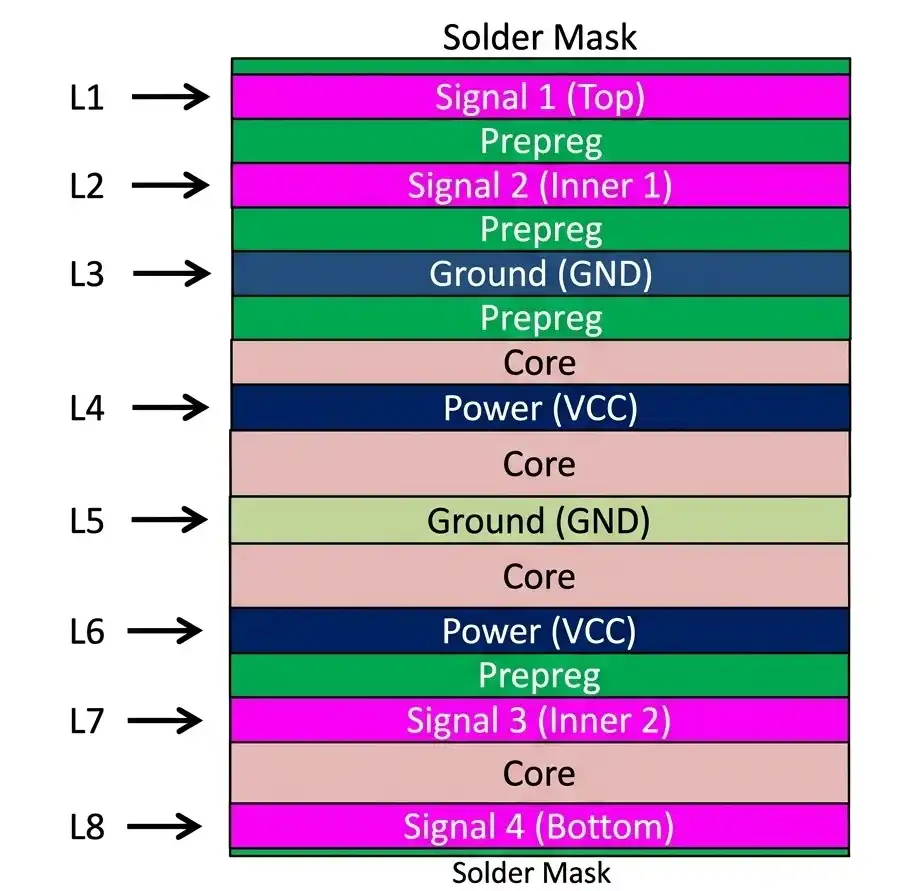

Example3: Low-Cost / Traditional Symmetric Type

This 8-layer PCB stackup uses a highly symmetrical structure. The middle layers alternate between GND and VCC planes, which makes the board stable and suitable for mass production. The main advantage is the strong symmetry of the stackup. It helps reduce PCB warpage during lamination and reflow soldering, improving SMT assembly yield. At the same time, the multiple power and ground layers create some interlayer capacitance, which helps stabilize the power distribution network (PDN) and reduce power noise.

However, the top and bottom signal layers do not have a nearby ground reference plane. This means weaker EMI shielding, so the structure is not ideal for very high-speed signals. In general, this stackup works well for medium-speed digital circuits, such as industrial control boards, MCU boards, and embedded systems. It is a good choice for projects that need lower cost and high structural stability.Click here to learn more about 8-layer stackup options.

How to Master Impedance Control in 8-Layer PCB Design

When designing an 8-layer PCB, impedance control mainly depends on the stackup structure, material parameters, and trace geometry. To calculate impedance correctly, you need to control several key variables:

- Dielectric thickness (H): the distance between the signal layer and the reference plane. A smaller distance results in lower impedance.

- Trace width (W): a wider trace results in lower impedance.You can use our online tool to calculate the trace width.

- Copper thickness (T): common values are 0.5 oz or 1 oz. Learn more about copper thickness.

- Dielectric constant (εr): determined by the base material. For example, FR-4 typically has an εr of about 4.2–4.5.

- Differential spacing (S): for differential pairs. Smaller spacing increases coupling and reduces differential impedance.

In practice, it is recommended to use industry tools to calculate the trace width and differential spacing, such as Polar SI9000 or Saturn PCB Toolkit.

The dielectric thickness between the signal layer and the reference plane is the most critical parameter for impedance control. A larger thickness leads to higher impedance. For this reason, PCB manufacturers usually provide a stackup parameter table during the design stage to ensure accurate impedance matching.

During routing, the following design rules are also important:

- Impedance traces should not cross a split in the reference plane (split plane). This can cause impedance discontinuity and affect signal integrity.

- Every via introduces parasitic capacitance and inductance, which can change the impedance. If a layer change is required, it is recommended to place a ground via next to the signal via to provide a proper return path.

After manufacturing, the PCB supplier usually performs TDR (Time Domain Reflectometry) testing to verify the impedance and ensure it stays within a tolerance of ±10% or ±5%.

Key Design Rules for 8-Layer High-Speed PCBs

To ensure stable performance of high-speed signals, the following design rules should be followed.

1. The 20H Rule

In high-frequency designs, the power plane can radiate electromagnetic noise. To reduce this effect, the edge of the power plane is usually pulled back from the ground plane by a distance of 20 × H (H is the dielectric thickness between the layers).

This structure keeps most of the electric field inside the ground plane area and helps reduce EMI radiation from the edges of the PCB.

2. Strict Stackup Symmetry

Your PCB stackup must be perfectly symmetrical from the center line. This includes copper weight, dielectric thickness, and material types. Symmetry prevents the board from warping during high-temperature reflow soldering, ensuring high SMT production yields.

3. Via Management & Layer Changes

When high-speed signals change layers, impedance continuity can easily be affected.

If a signal moves from the Top layer to the Bottom layer, a ground via should be placed close to the signal via. This provides a continuous return current path and reduces via inductance.

For very high-speed signals (such as >10 Gbps), back drilling is often used to remove the unused via stub. This helps reduce signal reflection and improves signal integrity.

4. Orthogonal Routing

Adjacent signal layers (such as Layer 3 and Layer 4) should use perpendicular routing directions.This layout reduces the overlapping area between traces on different layers and helps minimize broadside crosstalk.

5. Continuous Reference Planes

High-speed traces must always have a solid, unbroken reference plane directly underneath. Never route a high-speed signal across a split in the power or ground plane. Crossing a split forces the return current to take a long path, which ruins your eye diagram and increases interference.

Material Selection for 8-Layer PCB

In 8-layer PCB design, material selection is not only about cost. It is also a key factor that affects signal integrity and long-term reliability. As the layer count increases, the electrical performance and thermal stability of the PCB become more important.

Based on different application needs, materials for 8-layer PCBs can be divided into three categories:

| Type | Materials | Key Features | Applications |

|---|---|---|---|

| Standard Industrial | Isola 370HR IT-180A S1000-2M | High Tg (170°C–180°C), excellent thermal stability, compatible with lead-free soldering. | Industrial control, medical devices, and most standard high-speed PCBs (< 3GHz). |

| Mid-to-Low Loss | Panasonic Megtron 4/6 Isola TerraGreen Nelco N4000-13 | Low Df and stable Dk, suitable for high-speed serial signals. | Servers, storage networking, and telecom equipment (5Gbps – 20Gbps). |

| High Frequency / RF | Rogers 4350B Rogers 4003C | Excellent high-frequency performance and very low moisture absorption. Often used on the outer layers in hybrid stackups. | Radar systems, satellite communication, and 5G RF modules. |

To balance performance and cost, we often recommend a hybrid stackup solution. High-performance Rogers materials are used on the top and bottom layers where high-speed signals are routed, while the inner layers (usually power and ground planes) use lower-cost FR-4 materials.This design maintains the quality of critical high-speed signals while reducing the overall manufacturing cost by about 30%–50%.

Manufacturing Challenges

Manufacturing an 8-layer PCB is significantly more difficult than building a basic 4 or 6-layer board. As the layer count increases, the requirements for precision and reliability grow exponentially.

1. Inner Layer Registration

During lamination, all 8 layers of copper and prepreg must align perfectly. Even a microscopic shift can cause the drill to miss the copper pad (Annular Ring), leading to short or open circuits. Top-tier factories like HXD Circuit use LDI (Laser Direct Imaging) and CCD alignment systems to ensure every layer is perfectly synced before lamination.

2. Complex Lamination

An 8-layer board requires high heat and pressure to bond multiple materials together. If the stackup is asymmetrical or the pressure is uneven, the board will warp, making SMT assembly impossible. Poor cleaning or trapped air can also cause internal bubbles, leading to delamination later.

3. High Aspect Ratio Drilling

An 8-layer board is usually 1.6mm or thicker. As the board gets thicker and holes get smaller, the “Aspect Ratio” (thickness vs. hole diameter) increases. This makes drills prone to breaking and makes it hard for plating solution to reach the center of the hole. Precise speed control and high-penetration plating are essential for uniform copper walls.

4. Sequential Lamination for Blind & Buried Vias

Many 8-layer designs use blind or buried vias to save space. This requires the board to go through the lamination and drilling process multiple times. Every extra cycle increases the cost and the risk of yield loss.

5. Tight Impedance Tolerance

8-layer boards often carry high-speed signals like PCIe 4.0/5.0. Small changes in dielectric thickness or trace width will ruin the impedance. Manufacturers must have expert control over the Etch Factor and perform TDR (Time Domain Reflectometry) testing before shipping.

6. Inner Layer Adhesion

8-layer boards contain large power and ground planes. Smooth copper does not bond well to resin. To prevent the board from “popping” or exploding during soldering, we use Brown Oxide or black oxide treatments to roughen the copper surface and maximize bonding strength.

Conclusion

A successful 8-layer PCB project goes beyond the design files created in EDA software. To achieve stable impedance control and long-term reliability, you need a manufacturing partner who understands material selection (such as high-Tg laminates) and precise layer alignment processes.

At HXD Circuit, we specialize in complex multilayer PCB manufacturing and ensure your stackup meets strict IPC Class 2 or Class 3 standards. Whether you want to improve the power distribution network (PDN) or reduce crosstalk in HDI designs, our engineering team can support you from design review to high-yield production.

FAQS

How much more does an 8-layer PCB cost compared to 4- or 6-layer boards?

An 8-layer PCB usually costs about 20%–40% more than a 6-layer board, and even more compared to a 4-layer board. The cost increase mainly comes from:

-

Material usage: More copper, cores, and prepregs are required.

-

Process complexity: Longer lamination cycles, stricter layer alignment, and more drilling time.

-

Yield control: More layers make the board more sensitive to defects (like inner layer misalignment), increasing manufacturing difficulty.

What are some cost-saving tips for 8-layer PCB design?

You can optimize costs with the following methods:

-

Optimize panelization: Design the board size to maximize use of standard production panels (e.g., 18” x 24”).

-

Avoid over-design: Use through-hole vias instead of blind or buried vias unless routing is very dense.

-

Keep standard trace width: Maintain trace/space above 4 mil. While 3 mil is possible, tighter specs reduce yield and increase cost.

-

Surface finish selection: For non-high-speed or non-precision slots, OSP or standard ENIG is more cost-effective than thick gold or ENEPIG finishes.

What are the key factors affecting 8-layer PCB cost?

-

Base Material Selection – Standard FR-4 is cheaper. High TG materials (TG170, TG180) or low-loss materials (Rogers, Isola) for high-speed signals significantly increase cost.

-

Stackup & Board Thickness – The standard 1.6mm thickness is most economical. Special stackups, ultra-thin boards, or heavy copper increase cost due to more complex lamination.

-

Via Technology – Through-hole vias are the cheapest. Blind or buried vias require multiple drilling and lamination cycles, raising the cost.

-

Controlled Impedance – Strict impedance tolerance (e.g., ±5% or ±10%) for single-ended or differential signals requires extra impedance testing and process adjustments, adding technical service fees.

-

Surface Finish – HASL is cheapest, while ENIG or Hard Gold costs more but offers better flatness and solder reliability, making them common for 8-layer PCBs.

When should you upgrade from a 6-layer to an 8-layer PCB?

Consider upgrading to an 8-layer PCB in the following cases:

-

High signal integrity requirements: When trace density is high and a 6-layer board cannot provide complete reference planes for all critical signals.

-

High-speed interfaces: For DDR4/DDR5, PCIe Gen 4/5, or 10G+ Ethernet, finer impedance control is needed.

-

Strict EMC/EMI standards: 8 layers provide more shielding layers to reduce electromagnetic radiation and help pass certifications.

-

Complex power architecture: When the system has multiple voltage rails, extra power planes are needed to maintain power integrity (PI).

written by

steve ran

Senior Layout Manager